|

Bus Oddessy 2001

The overwhelming majority of this information was

derived from Micro Channel Architecture: Revolution in Personal Computing,

by Pat A. Bowlds, pages 135-137. ISBN 0-442-00433-8

Where did you go, Pat?

The beginning- The IBM 1401

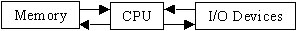

All I/O operations controlled are directly by the CPU.

The CPU was also responsible for information transfers to and from memory

or I/O devices. Many processing cycles were consumed with I/O management.

Throughput often limited by the speed of any I/O device, because the CPU

was forced to wait until an I/O operation was completebefore other activity

could begin.

I/O Processor Emerges- IBM System/360

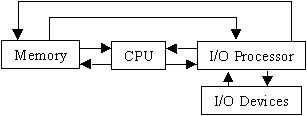

In 1964, the I/O Processor appears (as I do also). This

device boosted performance by allowing the CPU to delegate I/O management

to the I/O Processor by using high level commands. The I/O Processor then

managed all the data transfers between I/O and memory.

The I/O Processor was the ancestor to the channel architecture

used in IBM mainframes. Channels consist of an I/O Processor, multiple

I/O channels and their controllers. They are suitable for mainframe computing

with centralized storage and processing. In addition, the channels can

be cabled across the floor to meet a variety of peripheral requirements.

I/O Devices Use DMA- IBM System/7

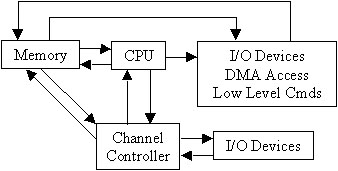

In the early 1970s (my God, that's before some of you

were BORN) the System/7 permitted I/O devices to have DMA. These first

uses of DMA by other devices other than the CPU was the foundation of today's

busmasters.

I/O devices were able to execute low-level commands from

the CPU. The Channel Controller has a similar function to the I/O Processor.

Data transfers from one I/O device to another required

many steps and involved the participation of several parties. At the time,

this resulted in significant performance gains by offloading more work

from the CPU onto I/O devices.

Smart I/O- IBM Series/1

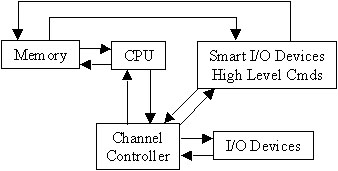

The Series/1 introduced the concept of intelligent adapters

(Smart I/O). These smart I/O devices interpreted and executed their own

commands, which gave them increased independence from the CPU. New software

protocols called Control Blocks were used to permit Series/1 adapters to

access memory directly (called first-party DMA operation) as well as communicate

with the channel controller.

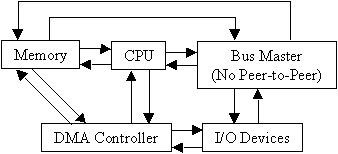

Fall From Grace- IBM AT

This hell-spawn bus continues to bedevil us with all sorts

of bad mojo. The channel controller was replaced by a DMA controller. The

DMA controller could take control of the I/O bus and act as a third party

in data transfers between devices and memory over multiple DMA Channels.

The AT's MASTER signal introduced the capability of bus

ownership by a Bus Master. This device was given direct memory access using

a single dedicated DMA channel. Problems with the AT implementation of

DMA include: no provision for peer-to-peer data transfer, arbitration by

multiple devices, preemption, and no defined method for equitable bus ownership.

It would have been possible for a bus master to gain control of the bus

and keep other devices from using it. If a bus master did hog the bus,

it would lead to lost data from the loss of memory refresh cycles.

It is possible to design a device and device driver to

prevent these problems, but designers rarely used the AT's MASTER signal.

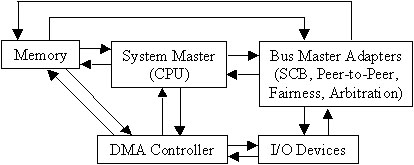

Supreme Being- IBM PS/2 Microchannel

In 1987, IBM blessed the hudled masses yearning for true

busmaster capabilities with MICROCHANNEL.

Unfortunately, IBM seemed to have wanted to rest after that.

True bus master capabilities were finally achieved with

a hardware mediated arbitration process, method of preemption, and a fairness

algorithm for equitable bus sharing.

A new protocol was defined- Subsystem Control Block Architecture,

which provides the proceedures for peer-to-peer communications and data

exchange between masters. SCBs provides a framework for the high level

command capabilities associated with the bus master function.

Busmaster Benefits

Busmasters offload functions from the system master, minimize

interrupts, provide their own processing power, and eliminate third party

DMA transfers. A busmaster goes to the memory or I/O slave (in addition

to other busmasters, of course) and gets the data it's looking for. Sort

of like a 200 pound mouse saying "Here, kitty, kitty".

Bus masters do not necessarily increase system performance.

If the system microprocessor is not busy with other tasks, and is very

powerful, an I/O slave implementation may be faster than a bus master implementation

with a less powerful processor. To Summarize- bus master performance

benefits are observed in systems in which the system microprocessor (or

I/O bus) is busy and near saturation.

Multiple CPU Subsystems

This is interesting for those questing for the "Superserver".

Busmasters can upgrade the processing capability of systems by adding a

new CPU subsystem that serves as a replacement of the system master. The

new CPU subsystem can be given control of the system resources after the

default master has initialized the system. The default master can be made

quiescent, relegated to supporting I/O functions, or operate concurrently

with the new CPU subsystem.

Because multiple bus masters are supported by microchannel,

multiple CPU subsystems can (with the appropriate operating system and

software support) operate concurrently. This concurrent process can provide

significant system processing cababilities without wasting any existing

system logic.

Processor Independence

The added CPU(s) can have a completely different software architectures

from that of their host system. Examples are the adapter for the IBM 6152

Academic System based on the RISC MC68881 CPU with 8MB on-board, Prometa

BusMaster WS/88K, based on the RISC 88000 and running UNIX System V, the

YARC Systems Micro 785+, based on the MC68020 at 40MHz and runs FORTRAN,

C, and Pascal, the Xtend Renaissance CPU board (details are coming, boards

inbound from Canada as of 29 Jun 00), the IBM PS/2 Wizard adapter, based

on the RISC i860 at 33MHz and running numeric intensive calculations (like

a big math-co!) and ending up with the darling of the bunch, the AOX/Kingston

MCMaster, based on a 386 or 486 from 25 to 33 MHz and running whatever

OS you want. Because microchannel architecture is SEPARATE

from the CPU architecture of the system, maximum design flexibility is

achieved.

9595 Main Page

|